IR2175 fun

Current problem is still to figure out how to get the 2175 working. It seems from tuesday's work that the analog side is receiving a signal. Is this being transferred correctly to the digital side?

Things are alot nicer today without the 7.5kHz whine, however at 50% duty cycle the current is a bit too high and the speed a bit too fast. I should try at 30%.

Okay that works and the speed is now 47Hz with PWM switching freq = 30kHz and duty cycle of 30%. I will try to do most of my tests with these settings.

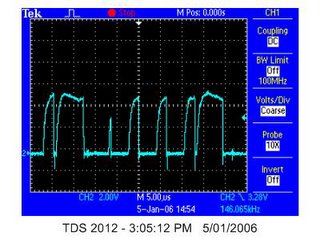

Time to see what the PO pin is doing.

This is a really messy output. Surely this should be a nice square wave that I can trust rather that this which will rely on the opto's charateristics as to where the actual cut off is. Maybe I have a cap in the wrong place?

Better check the other phases to see if this is a typical output.

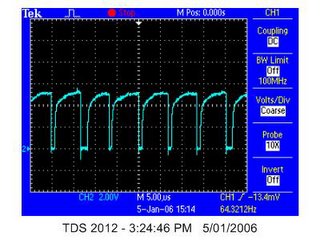

This is the PO pin for phase C. It shows similar slow transitions but does not seem to go as negative.

Looking at phase B:

it would seem from this that phase B is always saturating as the pulse width is always close to 91%. It is strange that the outputs are so different.

I had better check if it is the actual IR2175 chip so I will swap those from phases A and B.

Swapping chips does not change the output. It is clear now that A and C are similar in output and B seems to be saturating. This is strange as the resistance in each of the shunt resistors is the same (or very close). The difference possibly could be seen in the input, however for the time being, I will work with phase A to try and get it working.

Maybe it is something wrong with the sizing of the bootstrap capacitor?

Here is a plot of the bootstrap voltage V_B with reference to gnd - tomorrow I need to do further checks to see if this is the problem by measuring the V_BS voltage.

I JUST NOTICED THAT I HAD THE BRAKE MISALIGNED AND SO I AM NOW ABLE TO MOVE IT CLOSE TO THE DISK. THE SPEED IS NOW 44Hz.

I took a reading of the PO for phase A on one of the tracks that was further away from the chip and it was a lot more like that of phase B. Could my problems have to do with track layout?

Just done some more checking by measuring the pins as the signals leave the power board. I think that what I was measruing before was actually the B signal passing past the A chip. Best check the layouts more carfully next time.

Checking Resistors

R12, R13, R14, R15 are pullups and should be 10K - okay

R16, R17, R18, R19 are series resistors and should be 100R - actually 120R - okay

Just discovered that we have 2 lots of series resistors - should remove the 1k ones (R8,9,10,11)

removed these (replaced with a link) and the image looks pretty much the same. See phase A below:

Hopefully, however this will have fixed some of the problems with the signal not getting through to the intervace board.

Checking test points going into the power board connctor:

B, C and OC are fine, A is a little dodgy.

Checking inputs to optos

Same story, A was not coming through.

Problem traced back to the TP for A needed to be soldered on top as well as bottom.

Now it is time to check if I can read this waveform data in at the capture pin.

added a capture block - PWM must use timer 1 as I had to use timer 2. I hope that that does not mean that module B uses timer 2 - then I would be stuffed.

Could not get much sense out of the capture block - try again tomorrow.

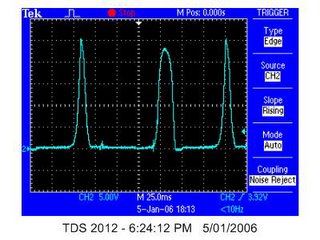

Time to try a high duty cycle with the 30kHz PWM freq before I go. It looks evil, need to understand why it looks this way.

0 Comments:

Post a Comment

<< Home